はんだ材料

J-STD-002(部品はんだ付性)

J-STD-002:はんだ付け性試験(部品)

部品リード、電極、ラグ、端子およびワイヤーのはんだ付け性試験

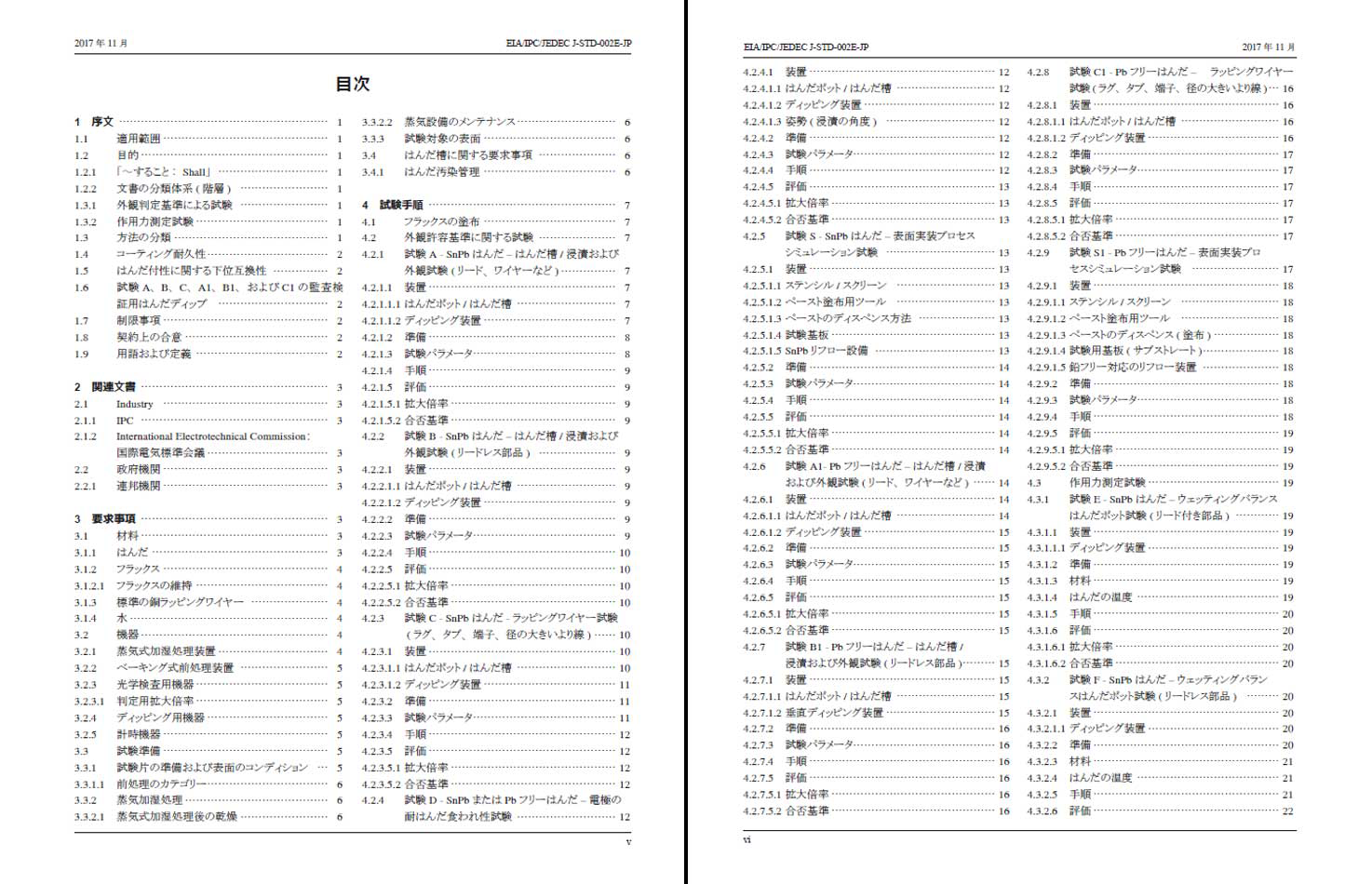

IPC-J-STD-002は、電子部品のリード、ターミネーション、単線、より線、ラグ、およびタブのはんだ付け性を評価するための試験方法、欠陥の定義、許容基準を規定し、またイラストを示すものである。

また、IPC-J-STD-002の規格には、はんだ食われ/はんだはじきに対する耐性の試験方法も含まれている。IPC-J-STD-002はサプライヤーおよびユーザーの両者による使用を目的としている。

IPC-J-STD-002Eの規格は次の三つの組織によって開発された:IPC、ECIA (電子部品産業協会)、JEDEC(半導体技術協会)。

本規格は、エレクトロニクス業界内で採用されるはんだ付け性試験の要求事項と試験方法を規定する2つの基準のうちの1つである。もう1つは、プリント基板側のはんだ付性について言及している。

J-STD-002のサンプル

最新日本語版バージョン:E

更新年:2017年

全65ページ

David Adams, Rockwell Collins

Dominik Alder, Lockheed Martin

Chris Ball, Valeo Inc.

James Bielick, IBM Corporation

Thomas Carroll, Boeing Company

Richard Davidson, Honeywell

Miguel Dominguez, Continental

更新年:2017年

全65ページ

David Adams, Rockwell Collins

Dominik Alder, Lockheed Martin

Chris Ball, Valeo Inc.

James Bielick, IBM Corporation

Thomas Carroll, Boeing Company

Richard Davidson, Honeywell

Miguel Dominguez, Continental

Donald Gerstle, Google Inc.

Todd Jarman, L-3 Communications

Udo Welzel, Robert Bosch GmbH

Jeffery Kukelhan, BAE Systems

Todd MacFadden, Bose Corporation

James Maguire, Intel Corporation

Michael Moore, U.S. Army

Fujiang Sun, Huawei Technologies

Toshiyasu Takei, Japan Unix Co., ltd.

Brian Toleno, Microsoft Corporation

Martin Wickham, NPL

Todd Jarman, L-3 Communications

Udo Welzel, Robert Bosch GmbH

Jeffery Kukelhan, BAE Systems

Todd MacFadden, Bose Corporation

James Maguire, Intel Corporation

Michael Moore, U.S. Army

Fujiang Sun, Huawei Technologies

Toshiyasu Takei, Japan Unix Co., ltd.

Brian Toleno, Microsoft Corporation

Martin Wickham, NPL

English

English 中文

中文 Deutsch

Deutsch Español

Español